# Toshiba NAND Flash Reliability Note

Date: Nov. 21, 2016

### 15nm MLC NAND Flash Reliability Note

#### Write/Erase Endurance

Write/Erase endurance failures may occur in a cell, page, or block, and are detected by doing a status read after either an auto program or auto block erase operation. The cumulative bad block count will increase along with the number of write/erase cycles.

|     | Write/Erase Cycles (Cycles) | Cumulative Block Failure Rate |

|-----|-----------------------------|-------------------------------|

| MLC | 3,000                       | Less than 0.04                |

#### **Data Retention**

The data in memory may change after a certain amount of storage time. This is due to charge loss or charge gain. After block erase and reprogramming, the block may become usable again.

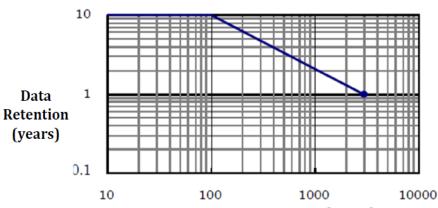

Here are the combined characteristics of Write/Erase Endurance and Data Retention.

| Write/Erase<br>Cycles (Cycles) | Estimated Data<br>Retention (Years) |

|--------------------------------|-------------------------------------|

| Initial<br>(Less than 100)     | 10                                  |

| 3,000                          | 1                                   |

#### **Condition of Data Retention Estimate:**

- Vcc=3.3V, Ta=40 °C, ECC=40bit/1KB

- All Pages in blocks are tested with Random data

- DUT = Toshiba 15nm MLC

Write / Erase Endurance (Cycles)

# 15nm Pseudo SLC (pSLC) Reliability Note

#### Write/Erase Endurance

Write/Erase endurance failures may occur in a cell, page, or block, and are detected by doing a status read after either an auto program or auto block erase operation. The cumulative bad block count will increase along with the number of write/erase cycles.

|      | Write/Erase Cycles (Cycles) | Cumulative Block Failure Rate |

|------|-----------------------------|-------------------------------|

| pSLC | 30,000                      | Less than 0.04                |

#### **Data Retention**

The data in memory may change after a certain amount of storage time. This is due to charge loss or charge gain. After block erase and reprogramming, the block may become usable again.

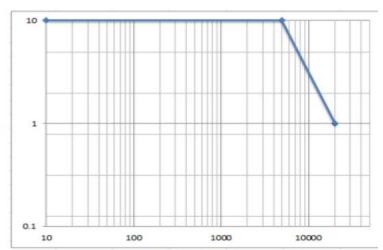

Here are the combined characteristics of Write/Erase Endurance and Data Retention.

| Write/Erase<br>Cycles (Cycles) | Estimated Data<br>Retention (Years) |

|--------------------------------|-------------------------------------|

| Initial<br>(Less than 100)     | 10                                  |

| 30,000                         | 1                                   |

Data Retention (years)

Write / Erase Endurance (Cycles)

#### **Condition of Data Retention Estimate:**

- Vcc=3.3V, Ta=40 °C, ECC=40bit/1KB

- All Pages in blocks are tested with Random data

- DUT = Toshiba 15nm pSLC

## 24nm SLC NAND Flash Reliability Note

#### **Write/Erase Endurance**

Write/Erase endurance failures may occur in a cell, page, or block, and are detected by doing a status read after either an auto program or auto block erase operation. The cumulative bad block count will increase along with the number of write/erase cycles.

|     | Write/Erase Cycles (Cycles) | Cumulative Block Failure Rate |

|-----|-----------------------------|-------------------------------|

| SLC | 100,000                     | Less than 0.04                |

#### **Data Retention**

The data in memory may change after a certain amount of storage time. This is due to charge loss or charge gain. After block erase and reprogramming, the block may become usable again.

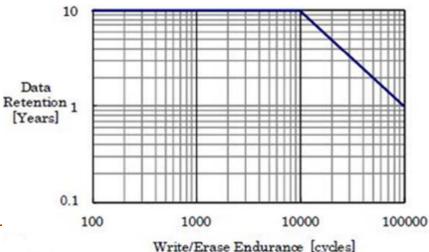

Here are the combined characteristics of Write/Erase Endurance and Data Retention.

| Write/Erase<br>Cycles (Cycles) | Estimated Data<br>Retention (Years) |

|--------------------------------|-------------------------------------|

| Initial<br>(Less than 100)     | 10                                  |

| 30,000                         | 3                                   |

| 100,000                        | 1                                   |

#### **Condition of Data Retention Estimate:**

- Vcc=3.3V, Ta=40 °C, ECC=40bit/1KB

- All Pages in blocks are tested with Random data

- DUT = Toshiba 24nm SLC

# Thank you